페이징 시스템(paging system)

페이징(paging) 개념

크기가 동일한 페이지로 가상 주소 공간과 이에 매칭하는 물리 주소 공간을 관리

하드웨어 지원이 필요

ex) Intel x86시스템(32bit)에서는 4KB, 2MB, 1GB 지원

리눅스에서는 4KB로 paging

페이지 번호를 기반으로 가상 주소/물리 주소 매핑 정보를 기록/사용

메모리에 page 단위로 up, load

프로세스(4GB)의 PCB에 Page Table 구조체가 가르키는 주소가 들어있다.

Page Table에는 가상 주소와 물리 주소간 매핑 정보가 있다.

참고) computer structure virtual memory

VPN: Virtual Page Number

Disk+Main memory 모든 저장 공간에 작업중인 process 저장

각 processs는 리눅스 기준으로 2^32(4GB=2^20pages)_page=4KB

virtual address 32bit중 20bit는 페이지 주소를 가르킴 12bit는 페이지 내의 바이트를 가르킨다.

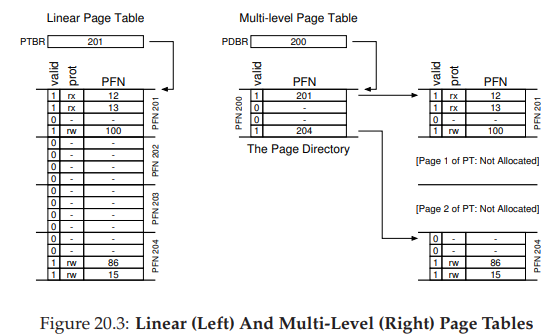

page table은 level1을 page directory leve2를 page table이라고 부른다.

page dircetory의 각 32bit(1024개)는 level2 page table을 가르킨다.

page또는 page frame: 고정된 크기의 block(4KB)

paging system

가상주소v=(p, d)

p: 가상 메모리 페이지

d: p안에서 참조하는 위치(offset)

ex) 페이지 크기가 4KB

가상 주소의 0-11비트가 변위(d)를 나타내고(12bit=4KB)

12이상이 페이지 번호가 될 수 있다. ->p에 실제 메모리의 해당 데이터 위치

참조)

프로세스가 4GB로 사용하는 이유- 32bit 시스템에서의 2의 32승이 4GB

Page Table

물리주소에 있는 페이지 번호와 해당 페이지의 첫 물리 주소 정보를 매핑한 표

가상주소 v=(p, d)라면

p: 페이지 번호

d: offset

paging system 동작

해당 프로세스에서 특정 가상 주소 엑세스 할려면,

해당 프로세스의 page table 에 해당 가상 주소가 포함된 page번호가 있는지 확인

page번호가 있으면 이 page가 매핑되 첫 물리 주소를 알아내고(p’)

p’+d가 실제 물리 주소가 된다.

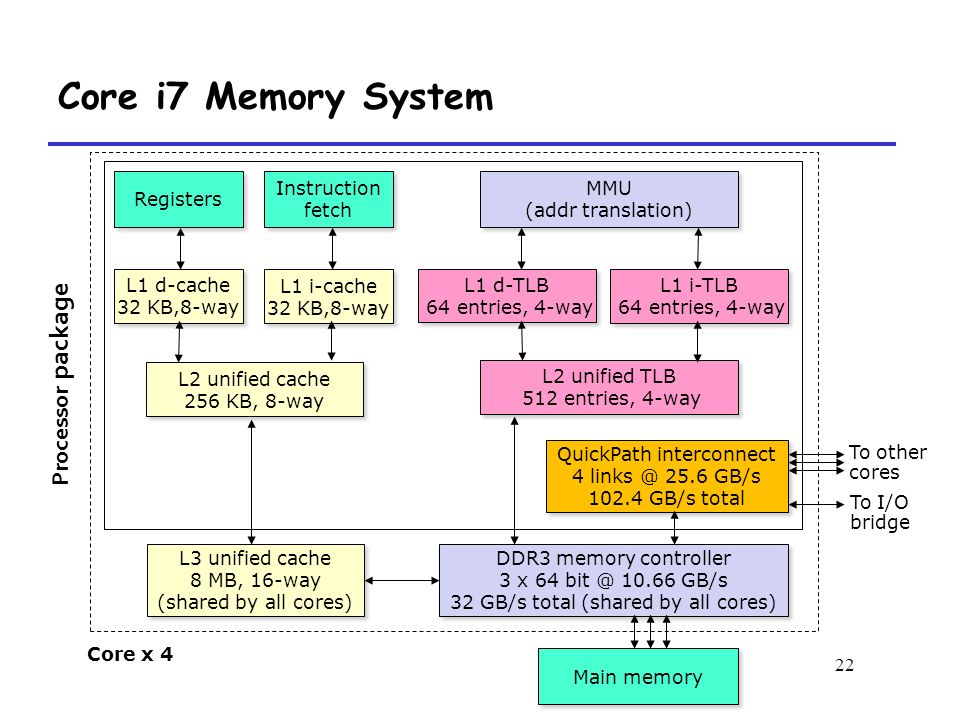

페이징 시스템과 MMU

CPU는 가상 주소 접근시

MMU 하드웨어 장치를 통해 물리 메모리 접근

프로세스 생성시, 페이지 테이블 정보 생성

PCB등에서, 해당 페이지 접근이 가능하고, 관련 정보는 물리 메모리에 적재(main mermory에 페이지 테이블 생성)

프로세스 구동시, 해당 페이지 테이블 base 정보가 별도 레지스터에 저장(CR3)

CPU가 가상 주소 접근시, MMU가 페이지 테이블 base 주소를 접근해서, 물리 주소를 가져옴

프로세스가 실행되면 레지스터에 해당 프로세스의 페이지 테이블 정보가 레지스터(CR3)에 저장된다.

2. TLB에 Virtual address entry가 올라와 있는지 확인(cache)

3. 있으면 바로 Memory에서 access 해서 데이터에 접근

4. 없으면 Memory의 TTB부터 위치해 있는 Page table에서 physical address 구해옴

5. 다시 Memory에 access해서 데이터 접근

메모리에 virtual address table이 있기 때문에 TLB를 Cache를 통해 빠르게 주소 알 수 있다.